GPIO Interface

1. GPIO Overview

GPIO stands for General Purpose I/O, which refers to universal input/output ports. Simply put, these are pins controllable by the MCU/CPU. These pins typically serve multiple functions, with the most fundamental being high/low level input detection and output. Some pins are also bound to on-chip peripherals of the microcontroller, serving as communication pins for interfaces like UART, I2C, SPI, or voltage detection functions.

2. GPIO Naming Convention

The ID of a Rockchip pin is composed of the controller (bank), port, and pin index.

- The number of controllers is consistent with the number of GPIO controllers.

- Ports are fixed as A, B, C, and D, with each port containing only 8 indexes (A=0, B=1, C=2, D=3).

- The index numbers are fixed as 0, 1, 2, 3, 4, 5, 6, 7.

The RK3568 is equipped with 5 GPIO controllers, each capable of managing 32 IO pins. When configured as GPIO functions, the port behavior is determined by the GPIO controller registers.

Tips

GPIO1_A4 indicates Controller Bank 1, Port A, and Index 4.

The pin number is calculated using the formula:

32 (pins per controller) × 1 (bank) + 0 (port offset within bank) × 8 (pins per port) + 4 (index) = 36.

3. Using the GPIO sysfs interface to control input/output operations

Command-line method

In Linux, the most common method for GPIO read/write operations is through the GPIO sysfs interface, which involves manipulating files such as export, unexport, gpio{N}/direction, and gpio{N}/value (with {N} replaced by the actual pin number) under the /sys/class/gpio directory. This approach is frequently employed in shell scripts. Starting from kernel version 4.8, support for libgpiod was introduced, and the legacy sysfs-based access method is gradually being deprecated.

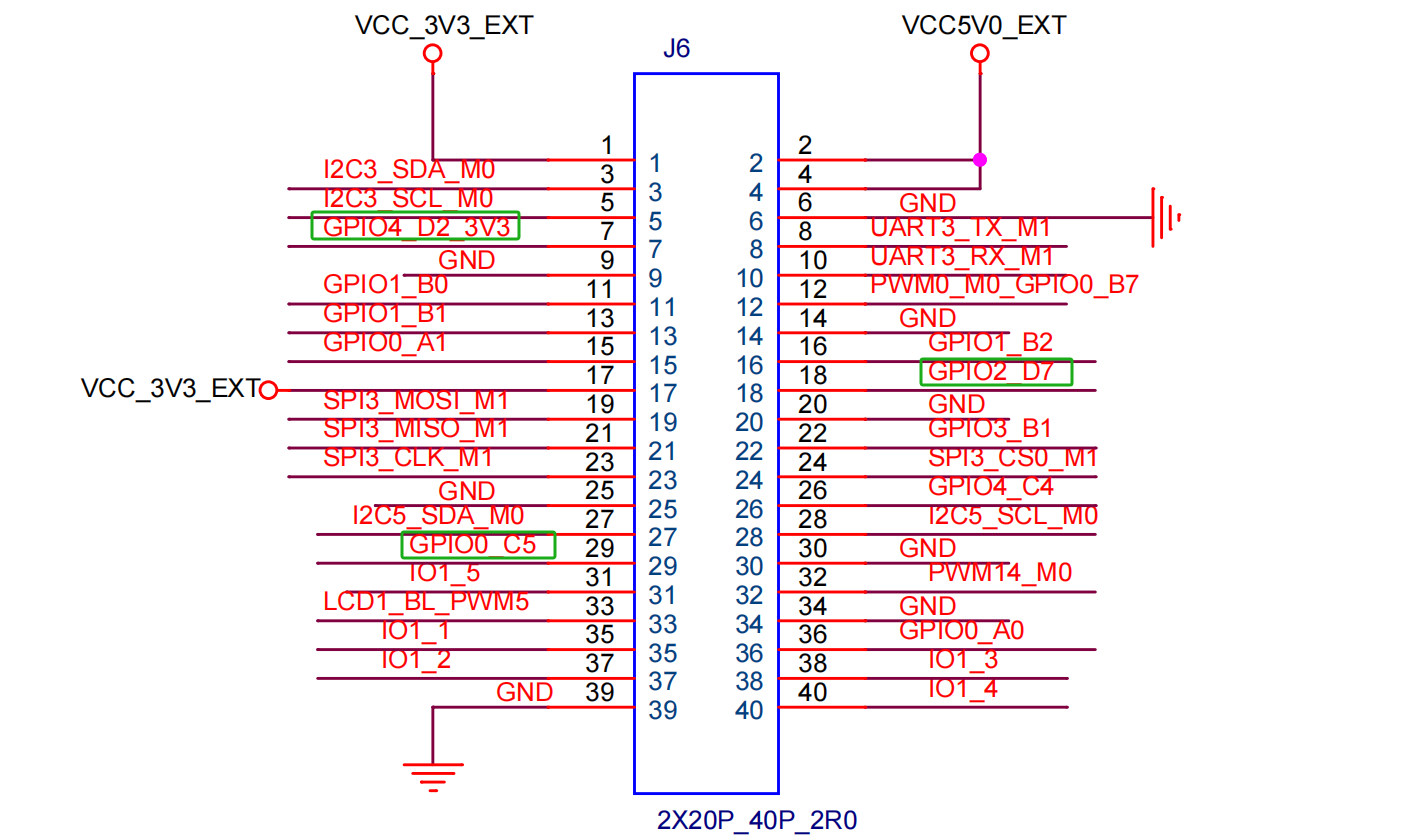

Taking the SC-3568HA as an example, select 3 GPIO pins from the 40-pin header.

| GPIO | Controller | Port number | Index number | Calculation result | PIN |

|---|---|---|---|---|---|

| GPIO4_D2 | 4 | D | 2 | 154 (32 x 4 + 8 x 3 + 2) | 7 |

| GPIO2_D7 | 2 | D | 7 | 95 (32 x 2 + 8 x 3 + 7) | 18 |

| GPIO0_C5 | 0 | C | 5 | 21 (32 x 0 + 8 x 2 + 5) | 29 |

#All the following operations require administrator privileges to be enabled (HarmonyOS has administrator privileges enabled by default).

#Enable GPIO4_D2 pin

echo 154 > /sys/class/gpio/export

#Set the pin to input mode

echo in > /sys/class/gpio/gpio154/direction

#Read the pin value

cat /sys/class/gpio/gpio154/value

#Set the pin to output mode

echo out > /sys/class/gpio/gpio154/direction

#Set the pin to low level

echo 0 > /sys/class/gpio/gpio154/value

#Set the pin to high level

echo 1 > /sys/class/gpio/gpio154/value

#Reset pin

echo 154 > /sys/class/gpio/unexport4. Extend GPIO ports

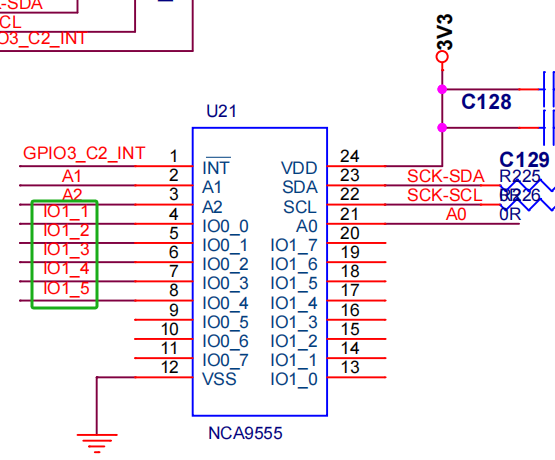

The SC-3568HA is equipped with the NCA9555 chip, a 24-pin CMOS device that provides 16-bit general-purpose parallel I2C-bus GPIO input/output expansion functionality.

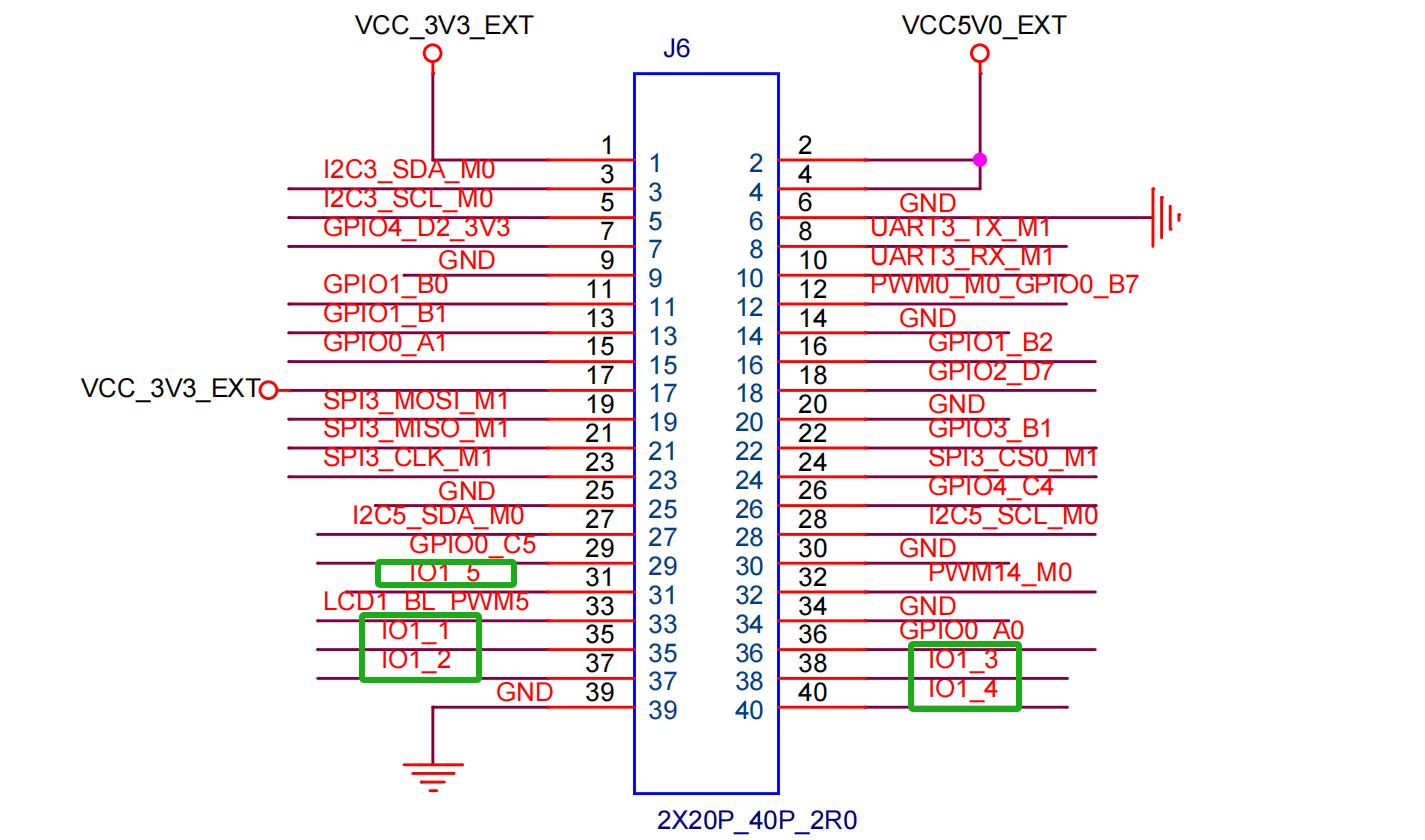

4.1 Extend GPIO port pins

Currently, 5 IOs are routed out from this chip for use and connected to a 40-pin connector.

| NCA9555 | 40PIN |

|---|---|

| IO1_1 | 35 |

| IO1_2 | 37 |

| IO1_3 | 38 |

| IO1_4 | 40 |

| IO1_5 | 31 |

4.2 Extend GPIO ports for use

This chip uses I2C communication, is mounted under I2C3, the driver files have been added, and the DTS configuration is as follows:

- /arch/arm64/boot/dts/rockchip/rk3568-toybrick-x0-linux.dts

&i2c3{

nca9555:nca9555@20{

reg=<0x20>;

compatible = "novosense,nca9555";

status="okay";

gpio-controller;

#gpio-cells = <2>;

};

};Tips

Using NCA9555's IO ports within the kernel is largely consistent with standard GPIO usage.

For example:

//Using standard GPIO

&vcc3v3_lcd0_n {

gpio = <&gpio0 RK_PC7 GPIO_ACTIVE_HIGH>;

enable-active-high;

};

//Using NCA9555's IO

&vcc3v3_lcd1_n {

gpio = <&nca9555 3 GPIO_ACTIVE_HIGH>; //Corresponding to NCA9555 IO0_3

enable-active-high;

};

&vcc3v3_lcd2_n {

gpio = <&nca9555 10 GPIO_ACTIVE_HIGH>; //Corresponding to NCA9555 IO1_2

enable-active-high;

};