07 FPGA FSPI Communication Case

1 Case Introduction

This case aims to run the Linux system on the ARM side and perform read and write tests on the FPGA DRAM through the FSPI bus.

2 Communication process between ARM and FPGA

Implementing SPI Master Function on ARM

Open the SPI device node: Open the /dev/spidev4.0 device node.

Configure the FSPI bus: Use the ioctl command to configure the polarity, phase, communication rate, data length and other parameters of the FSPI bus.

Select the transmission mode: You can choose single-line mode, two-line mode or four-line mode. When set to four-line mode, both data transmission and reception will adopt four-line mode. This case only supports four-line mode.

Data transfer: Send data to the FSPI bus and read data from the FSPI bus.

Verify data: Verify the transmitted data and then print out the read/write rate and bit error rate.

Implementing SPI Slave Function on FPGA

Data storage: FPGA saves the data sent by SPI Master to DRAM.

Data read: When the SPI Master initiates a data read request, the FPGA reads data from the DRAM and transmits it to the SPI Master through the FSPI bus.

3 Operation process

Open the terminal and copy the executable program smdt_spi_rw in the bin directory of this case (05-Development Materials\Software Development Materials\linux_demo\smdt_fpga_fspi_demo\bin) to the development board file system (the source code can be viewed in the src path).

#修改 Linux 内核日志的显示级别,内核的日志级别被设置为只显示紧急或更高级别的消息

echo 1 4 1 7 > /proc/sys/kernel/printkExecute the following command in the terminal to switch to the directory where the smdt_fpga_fspi_demo executable program is located

#切换到 smdt_fpga_fspi_demo 可执行程序所在目录

cd ‘the file's directory’

#查看 smdt_spi_rw 是否在该目录下

lsIf the executable file smdt_spi_rw is in the current directory, modify the permissions of the executable file

#修改文件权限

chmod 777 smdt_spi_rw

#查询是否修改成功

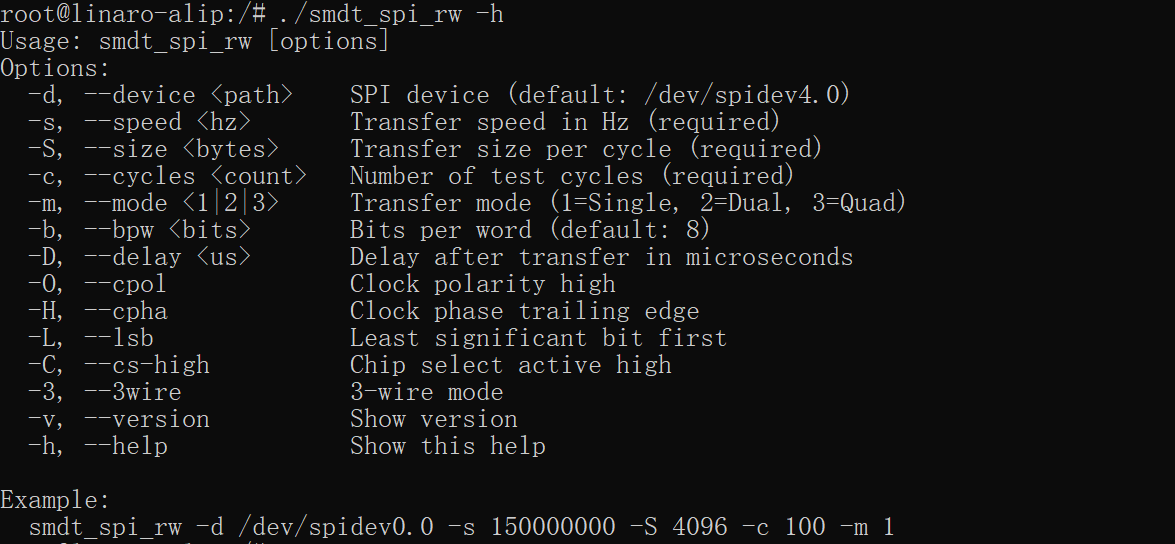

ls -ld smdt_spi_rwAfter confirming that the file modification permission is successful, execute ./smdt_spi_rw -h to view the help information of the program.

#查看帮助信息

./smdt_spi_rw -hThe execution result is as follows:

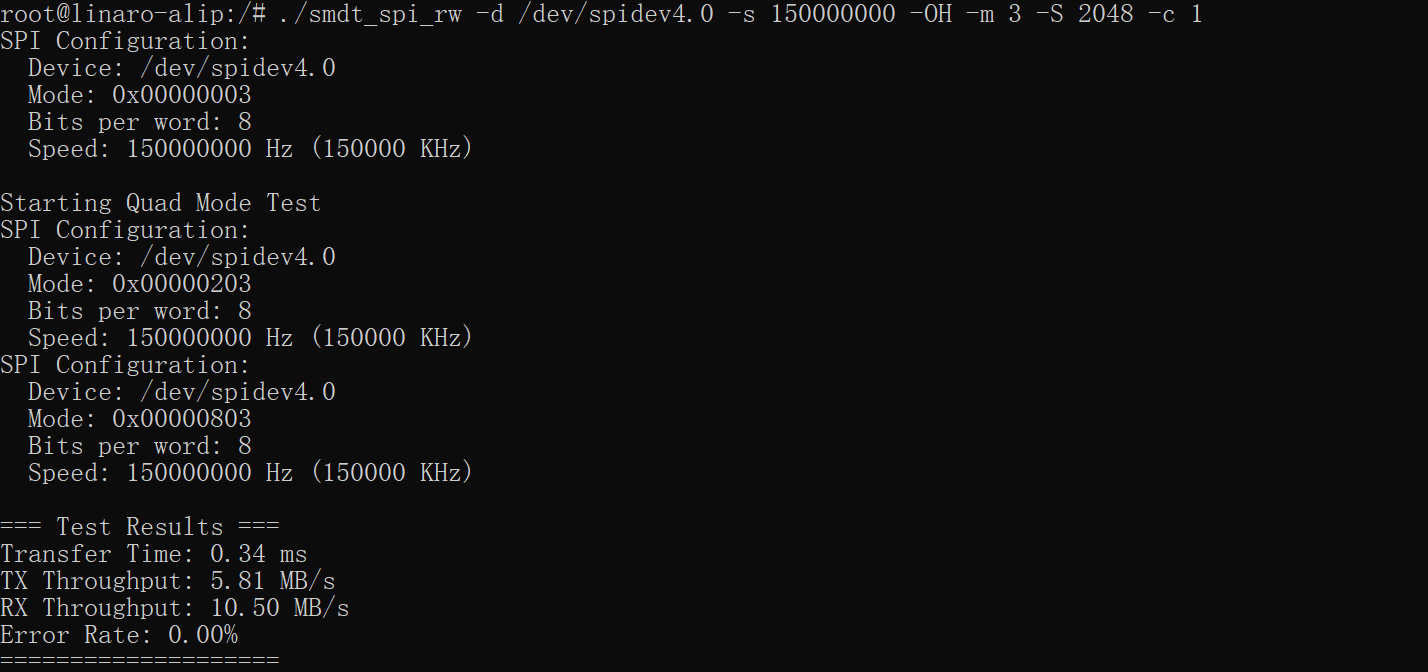

Functional testing

Enter the following instructions. On the ARM side, 2048 bytes of random data are written into the FPGA's DRAM via the FSPI bus configured in four-wire mode. The data is then read for verification and the read and write speed of the FSPI bus and the calculated bit error rate are printed out. The execution results are shown in the figure below.

./smdt_spi_rw -d /dev/spidev4.0 -s 150000000 -OH -m 3 -S 2048 -c 1

# The parameters are explained as follows:

# `-d`:Used to specify the device node.

# `-s`:Used to set the frequency of the communication clock, with the unit being hertz (Hz).

# `-O`:Represents clock polarity inversion, i.e., CPOL (Clock Polarity) is set to 1.

# `-H`:Indicates that data is sampled on the second edge at the start of the clock cycle, i.e., CPHA (Clock Phase) is set to 1.

# `-m`:Selects the transmission mode, where 1 represents single-wire mode, 2 represents dual-wire mode, and 3 represents four-wire mode.

# `-S`:Sets the size of the transmitted data, with the unit being bytes (Byte).

# `-c`:Sets the number of times to cyclically transmit data packets.

As can be seen from the above figure, the measured write rate is 5.81 MB/s, the read rate is 10.5 MB/s, and the bit error rate is 0.00%.

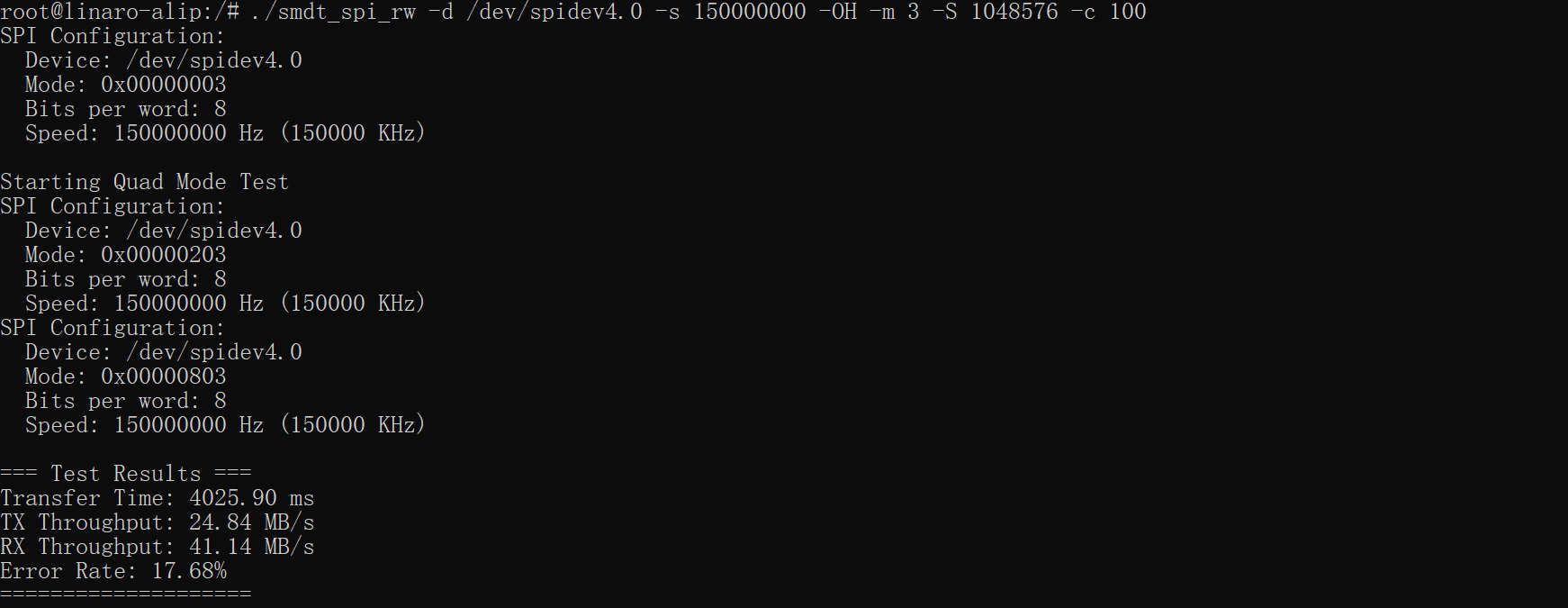

Performance Testing

When performing performance testing, the communication clock frequency of the FSPI bus needs to be set to 150MHz. Under this setting, ARM will write 1MB of random data to the FPGA's DRAM through the FSPI bus, then read the data, and repeat this process 100 times. No data verification is performed during the test, and the read and write speed and error rate of the FSPI bus will be output in the end. The execution results are shown in the figure below. This case design reads and writes 2048Byte of random data to the FPGA DRAM at a time, so the bit error rate is high.

./smdt_spi_rw -d /dev/spidev4.0 -s 150000000 -OH -m 3 -S 1048576 -c 100